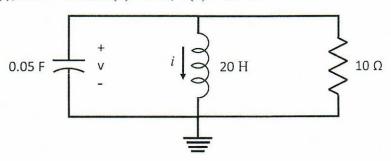

For the following circuit,

a) Determine the Source-Free response, v(t), for t > 0. Let i(0) = 2 A, v(0) = 60 V.

Quadratic eq:  $s = \frac{-b \pm \sqrt{b^2 - 4ac}}{2a}$

b) Is the circuit (Overdamped \ Critically Damped \ Underdamped - Circle One)?

v(t) =

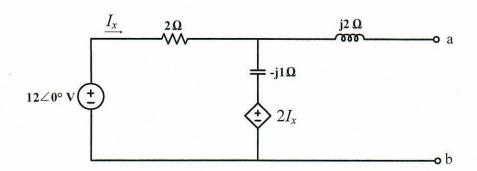

For the circuit shown below

- (a) Calculate the Thevenin voltage across nodes a and b ( $V_{TH}$ ).

- (b) Calculate the Thevenin impedance across nodes a and b  $(Z_{TH})$ .

An op-amp is ideal except it has a finite open-loop gain of  $A_{OL} = 2 \times 10^3$ . The op-amp is connected in an inverting configuration.

- a. Sketch the circuit labeling the input resistor  $R_1$  and the feedback resistor  $R_2$ .

- b. Determine the resistor ratio  $\frac{R_2}{R_1}$  such that the closed-loop voltage gain is  $A_{CL}=-15.0$ .

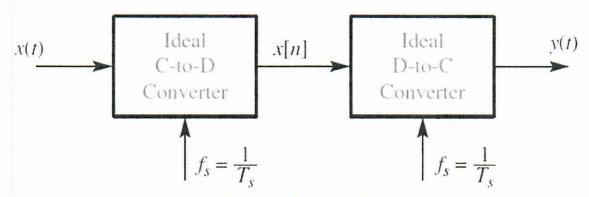

Refer to Fig. 1 for the system with ideal Continuous-to-Discrete (C-to-D) and Discrete-to-Continuous (D-to-C) converters.

Figure 1: Ideal C-to-D and D-to-C system.

- (a) Suppose that the output from the C-to-D converter is  $x[n] = \cos(0.2\pi n)$ , and the sampling rate of the C-to-D converter is  $f_s = 8000$  samples/s. Determine a formula for the continuous-time sinusoidal input x(t) using the smallest frequency greater than 10000 Hz.

- (b) Suppose the output from the C-to-D converter is  $x[n] = \cos(0.25\pi n)$ , the input signal is  $x(t) = \cos(510\pi t)$ , and the sampling rate (fs) of the C-to-D converter is less than 130 samples/s. Determine the largest possible sampling rate satisfying these three conditions.

- (i) Suppose the random variable x has a probability density function (pdf) f(x). Compute the cumulative distribution function of  $x^2$  and then find its probability density function.

- (ii) Work out the answer when the random variable x has a standard normal distribution  $(f(x) = \frac{1}{\sqrt{2\pi}}e^{-\frac{1}{2}x^2})$  to find the probability density function of the chi-square distribution.

Copyright © 2020 by the Contributing Control Area Faculty. All rights reserved. No part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the written permission of the copyright holder(s).

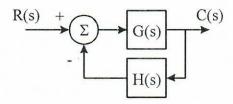

You are given the following system. Find the value of K for which the step response of the closed-loop system will have a 5% overshoot. For this value of K, calculate the  $T_p$ , the peak time and the  $T_s(2\%)$ , the time required for the system output to settle to within 2% of its final value.

$$G(s) = \frac{K}{s^2 + 1.5s}$$

$$H(s) = 1$$

Copyright © 2020 by the Contributing Control Area Faculty. All rights reserved. No part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the written permission of the copyright holder(s).

A discrete-time linear control system is described by

$$\mathbf{x}(k+1) = \begin{bmatrix} 1 & -1 \\ 0.2 & 0.5 \end{bmatrix} \mathbf{x}(k) + \begin{bmatrix} 1 \\ 0 \end{bmatrix} u(k)$$

$$y(k) = \begin{bmatrix} -0.4 & 0 \end{bmatrix} \mathbf{x}(k) + u(k),$$

Where u,  $\mathbf{x}$ , and y are the input, the state, and the output variables, respectively.

- (a) Determine the transfer function, Y(z)/U(z) of the system (50%)

- (b) Determine the state  $\mathbf{x}(2)$ , when  $\mathbf{x}(0) = \begin{bmatrix} 1 & -1 \end{bmatrix}^T$ , and  $u(k) = (-1)^k$  for all  $k \ge 0$ . Show all your work (50%).

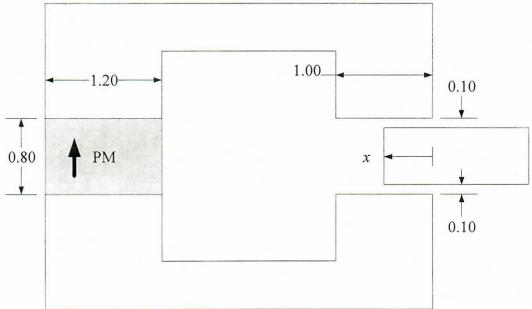

Consider the structure shown below in cross-section. The PM is SmCo, which can be modeled as having an equivalent coercivity of  $H_c' = -720 \, \mathrm{kA/m}$  and recoil permeability of  $\mu_R = 1.06 \, \mu_0$ . All dimensions are given in **centimeters**. Depth into the page is 3.0 cm. The steel is infinitely permeable. There are two air gaps, each with length 0.1 cm and area determined by depth into page and overlap, x. Neglect fringing. We want to find the force acting on the movable piece, for the case where  $0 \le x \le 1.0 \, \mathrm{cm}$ . Useful equations:

$$\mathcal{R} = \frac{\ell}{\mu A}$$

$$\mu_0 = 4\pi \times 10^{-7} \frac{H}{m}$$

$$W'_{fld} = \int_0^{i_1} \lambda_1 (\hat{i}_1, 0, \dots) d\hat{i}_1 + \int_0^{i_2} \lambda_2 (i_1, \hat{i}_2, 0, \dots) d\hat{i}_2 + \dots$$

$$f_{fld} = \frac{\partial W'_{fld} (i, x)}{\partial x}$$

$$(Ni)_{equiv} = -H'_c d$$

- a. Draw the magnetic equivalent circuit for the device. Convert the PM to a Thévenin equivalent. Find all components numerically (although you may not need the numbers for a while). Leave x as a free variable.

- b. Solve the MEC for the flux linkage for the equivalent coil.

- c. Determine the co-energy. At this point, you may have extraneous (non-physical) variables.

- d. Find the force on the movable member. At this point, the only allowable free variable is x.

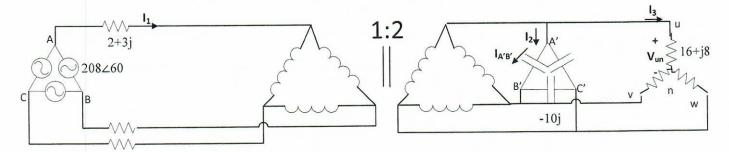

In the following circuit, find the following (both amplitude and angle):

- a)  $I_1$ ,  $I_2$ , and  $I_3$  (45 points).

- b) I<sub>A'B'</sub> (Capacitor current) (15 points).

- c) Phase voltage of the load (16+8j) equal to  $V_{un}$  (15 points).

- d) 3-phase complex power of the source (15 points)

- e) 3-phase complex power of the capacitor bank. (10 points)

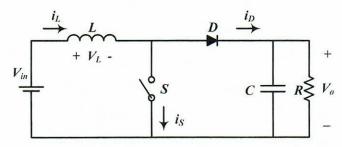

A Boost dc-dc converter has the following parameters:  $V_{in} = 400 \text{ V}$ , d = 0.25,  $V_{out} = 650 \text{ V}$ ,  $L = 100 \mu\text{H}$ , and  $f_{sw} = 100 \text{ kHz}$ .

- a) Find the peak value of the inductor current. (20 points)

- b) Accurately plot the waveform of the inductor current. (20 points)

- c) Find the average value of the inductor current. (20 points)

- d) Find the input power. (20 points)

- e) Find the value of the load resistor. (20 points)

In the system shown below, a solid line-ground fault occurs on bus 3. Both generators are solidly grounded.

What are the positive, negative and zero sequence fault currents in line 2-3? The prefault voltages are 1.0 per unit.

### Waves/Devices

Student Code\_\_\_

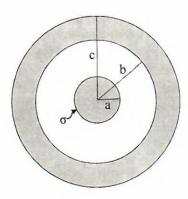

Metallic concentric shell. The figure on the right shows a cross-section of a coaxial cable (a metallic concentric shell). The diameters of the inner conductor, the inner wall of the outer conductor, and the outer wall of the outer conductor are a, b, and c, respectively. Consider a positive surface charge density  $\sigma$  at the surface of the inner conductor. A) Find the electric field everywhere as a function of radial distance r (r < a, a < r < b, b < r < c, and r > c). B) Please plot the electric field strength as a function of radial distance r. C) If the outer wall of the outer conductor is grounded, find the electric field at r > c.

Consider an antenna that has a directivity  $D=3~\mathrm{dBi}$  at 1 GHz in a certain direction. Total antenna efficiency  $\varepsilon_a=50~\%$ . Determine the voltage a plane wave with the amplitude of 1 V/m, illuminating the antenna from the direction the directivity is given for, will induce at the 50 Ohm resistor attached to the antenna port (assume that the polarization of the plane wave matches the polarization of the antenna, i.e. the polarization mismatch is irrelevant).

Useful formulas:

Power received by the antenna is

$$P_{received} = S_{inc}A_e$$

where  $S_{inc}$  is the incident power density,

$$A_e = \frac{\lambda^2}{4\pi} G$$

is the effective aperture of the antenna,

$$G = \varepsilon_a D$$

is the antenna gain.

1. [40%] An abrupt silicon p-n junction diode has a net acceptor concentration 10<sup>17</sup>cm<sup>-3</sup> in the p-side and a net donor concentration 10<sup>15</sup>cm<sup>-3</sup> in the n-side, respectively. Calculate the potential difference across the depletion region (or space charge region) at thermal equilibrium (i.e. contact potential or built-in potential) in room temperature (300K).

| Constants*                    | Equations*                                                                                                                                                                                                                                                                  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ■ kT = 0.0259 [eV] (at 300 K) | $\begin{array}{ll} \bullet & n_o  p_o = n_i^2 \\ \bullet & n_o = n_i  exp[(E_F - E_i)  /  kT]  or  (E_F - E_i) = kT  \ln(n_o/n_i) \\ \bullet & p_o = n_i  exp[(E_i - E_F)  /  kT]  or  (E_i - E_F) = kT  \ln(p_o/n_i) \\ \bullet & \sigma = q(n\mu_n + p\mu_p) \end{array}$ |  |

<sup>\*</sup> Definitions of parameters are not given for the provided information. It is expected that the examinees interpret the meaning.

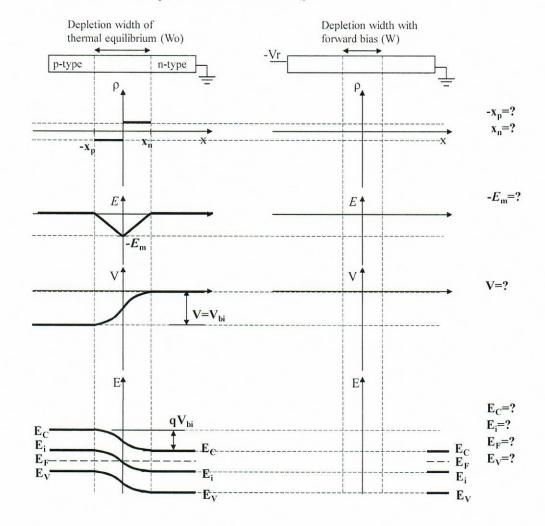

- 2. [60%] Complete the diagrams and indicate all question-marked items of the forward-biased symmetric p-n junction (i.e. Show the expected difference when the bias is applied). Assume the n-side is electrically grounded. The dashed lines serve only as "reference lines" to indicate the value of each item in its thermal equilibrium condition.

- (distance x, charge density  $\rho$ , electric field E, voltage V, charge q, electron energy E, bottom level of conduction band  $E_C$ , intrinsic level  $E_i$ , Fermi level  $E_F$ , top level of valence band  $E_V$ ,)

**Computational Intelligence**

Student Code\_\_\_\_

Describe the advantages and disadvantages of Extreme Learning Machines vs. another machine learning method of your choice, using math and your explanations.

**Computational Intelligence**

Student Code\_\_\_\_

Describe memory intensive approaches available for machine learning, and what new ones will be available soon. Focus particularly on the advantages and disadvantages of the approaches you are describing.

**Computational Intelligence**

Student Code\_\_\_\_

Explain Adaptive Resonance Theory in all the detail you can, using math, figures and your explanations.

## **Computer Architecture & Embedded Systems**

Student Code\_\_\_\_

The table below shows instruction-type breakdown for different programs:

|           | # of Instructions |      |       |        |       |

|-----------|-------------------|------|-------|--------|-------|

|           | Compute           | Load | Store | Branch | Total |

| Program 1 | 1000              | 400  | 100   | 50     | 1550  |

| Program 2 | 1500              | 300  | 100   | 100    | 1750  |

- a. Assuming that compute instructions take 1 cycle per instruction, load and store instructions take 10 cycles per instruction, and branch instructions take 3 cycles per instruction, find the execution time of each program on a 3GHz processor.

- b. Find the average CPI (clock cycles per instruction) of each program using the values given in a.

- c. Assuming that compute instructions take 1 cycle per instruction, load and store instructions take 2 cycles per instruction, and branch instructions take 3 cycles per instruction, what is the speed-up of a program if the number of compute instructions can be reduced by one-half?

### **Computer Architecture & Embedded Systems**

Student Code\_\_\_\_

When adding two n-bit signed (2's complement) binary numbers A and B, the following Boolean expression can be used to detect overflow where a<sub>i</sub> and b<sub>i</sub> are bits at bit position i in A and B, and s<sub>i</sub> is the sum bit at bit position i:

$$OV = a_{n-1} \cdot b_{n-1} \cdot \overline{s_{n-1}} + \overline{a_{n-1}} \cdot \overline{b_{n-1}} \cdot s_{n-1}$$

A simpler formula for overflow detection is given as:

$$OV = c_n \oplus c_{n-1}$$

where c<sub>n-1</sub> and c<sub>n</sub> are the carry-in and carry-out of the leftmost full adder.

Prove that this simpler formula is equivalent to the previously given formula by showing the following two cases are equivalent to two product terms in the previously given formula:

Case 1: 0 carried in, and 1 carried out.

Case 2: 1 carried in, and 0 carried out.

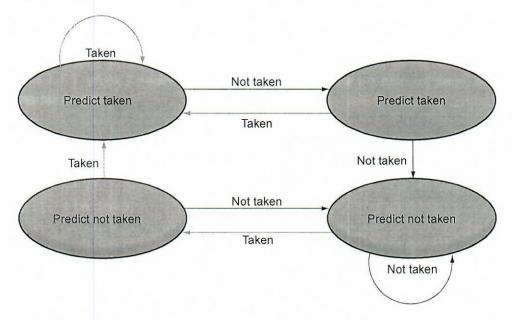

Consider the dynamic branch predictor given below. Calculate the branch prediction accuracy ratio (= total number of correct branch predictions / total number of branch predictions) for the following branching pattern: T-T-T-N-N-T-N-N-T-T-T-N-N-T-T-T-T, where T means a branch taken and N means a branch not taken. Assume that the starting state is one at the top-left corner.

## **Computer Architecture & Embedded Systems**

Student Code\_\_\_\_

Here is a series of address references given as word addresses: 2, 3, 11, 16, 21, 13, 64, 48, 19, 11, 3, 22, 4, 27, 6 and 11. Assuming a direct-mapped cache with 8 one-word blocks that is initially empty, label each reference in the list as a hit of a miss and show the final contents of the cache.

Using the series of references given in the previous problem, show the hits and misses and final cache contents for a fully-associative cache with 8 one-word blocks that is initially empty. Assume "first-in, first-out" replacement strategy.

Implement a synchronous sequential circuit to output the sequence 57315731... with an enable input (E) such that the next digit in the sequence is output when E = 1 and the current digit is output when E = 0. Implement this machine using D flip flops by using the truth table on this page and the K-maps on this and the following pages. Take advantage of any don't cares that come up. Finally, implement the circuit on the page following the K-maps.

| EN | $Q_2Q_1Q_0$ | $D_2D_1D_0$ |  |

|----|-------------|-------------|--|

| 0  | 000         |             |  |

| 0  | 001         |             |  |

| 0  | 010         |             |  |

| 0  | 011         |             |  |

| 0  | 100         |             |  |

| 0  | 101         |             |  |

| 0  | 110         |             |  |

| 0  | 111         |             |  |

| 1  | 000         | 000         |  |

| 1  | 001         |             |  |

| 1  | 010         |             |  |

| 1  | 011         |             |  |

| 1  | 100         |             |  |

| 1  | 101         |             |  |

| 1  | 110         |             |  |

| 1  | 111         |             |  |

| D2 =  |  |

|-------|--|

| 11/ - |  |

|       |  |

| Q1 Q0 | 00 | 01 | 11 | 10 |  |

|-------|----|----|----|----|--|

| 00    |    |    |    |    |  |

| 01    |    |    |    |    |  |

| 11    |    |    |    |    |  |

| 10    |    |    |    |    |  |

# Integrated Circuits & Logic Design

Student Code\_\_\_\_

D1 = \_\_\_\_\_

| Q1 Q0 | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    |    |    |    |    |

| 01    |    |    |    |    |

| 11    |    |    |    |    |

| 10    |    |    |    |    |

D0 =

| Q1 Q0 | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

|       |    |    |    |    |

| 00    |    |    |    |    |

|       |    |    |    |    |

| 01    |    |    |    |    |

|       |    |    |    |    |

| 11    |    |    |    |    |

|       |    |    |    |    |

| 10    |    |    |    |    |

| 10    | 4  |    |    |    |

|       |    |    |    |    |

Integrated Circuits & Logic Design

Student Code\_\_\_\_

Draw the sequential circuit below.

Answer the follow questions.

a) Using OR-gates and/or NOR-gates along with a 3-to-8 decoder, implement the function  $f(a,b,c)=\sum m(0,1,5,6)$

b) Implement the function  $f(a,b,c,d) = \prod M(0,2,3,5,6,9,13,15)$  using an 8:1 multiplexer and inverters. You may use a single NOT gate in addition to the multiplexer.

Dynamic vs complementary (push-pull) logic.

a. Draw the transistor diagram for a (traditional) complimentary CMOS gate that performs the following function:  $out = \overline{A \cdot B \cdot (C + D)}$ . Include the size of FETs required to give approximately the same rise/fall time as a minimum sized inverter.

b. Draw the transistor diagram for a dynamic logic gate that performs the same function:  $out = \overline{A \cdot B \cdot (C + D)}.$  Include the size of FETs required to give approximately the same rise/fall time as a minimum sized inverter.

Answer the questions for parts a-c below.

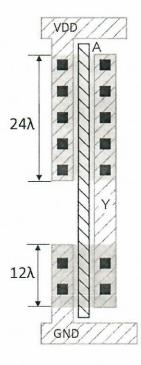

a. Sketch a transistor-level schematic of the below layout and annotate the transistor with its width.

- b. When a unit  $(4\lambda)$  transistor has diffusion capacitance C, calculate the total diffusion capacitance at the output node Y.

- c. When the layout in (a) is folded as shown below, calculate the total diffusion capacitance at the output node Y.

### Networking, Security & Dependability

Student Code\_\_\_

Consider the transmission of 4000-bit frames on a heavily loaded 50 kbps satellite channel. Each frame has 40 header and 3960 data bits. Assume the (one-way) signal propagation time from the earth to the satellite is 270 msec.

Assume that the stop-and-wait protocol is used, where the source transmits one frame, then waits to receive a 40-bit acknowledgement from the receiver before transmitting the next frame.

Answer all three parts below.

- 1. Calculate the line utilization. Fractional answers are acceptable.

- 2. Now assume that instead of stop-and-wait, a variant of the selective-repeat protocol is used, with a window size large enough to allow the source to transmit continually instead of stopping to wait for an acknowledgment. No acknowledgments are sent. If the destination receives a corrupt frame, it sends a 40-bit negative acknowledgement (NAK) frame. The error rate for data frames is 1%, and the error rate for NAK frames is negligible. Compute the fraction of the capacity that is wasted on overhead. Both headers and retransmissions count as overhead.

- 3. In part 2, what is the expected number of attempts required for successful transmission of a frame?

### Networking, Security & Dependability

Student Code

#### Answer all five questions below.

- 1. Does non-linearity make a cipher resistant to cryptanalysis or brute force attacks? Justify your answer.

- 2. Does computational security describe resistance to brute force or cryptanalytic attacks? Justify your answer.

- 3. The affine Caesar cipher replaces each plaintext character, p, with the ciphertext character, C, determined by the following equation:  $C = E([a, b], p) = ap + b \mod N$ .

- a and b are a pair of integers that act as the key. N is the size of the alphabet.

- The fundamental requirement for any cipher is reversibility, i.e., that it create a one-to-one mapping between each plaintext character and the ciphertext character to which it is encrypted. Mathematically, this implies that p = q if and only if E(p) = E(q). Does this requirement place any restrictions on the value of a for the affine Caesar cipher? What about b? Justify your answers.

- 4. Describe the brute force approach to breaking this cipher. In this approach, every possible key is tried until the decryption yields an intelligible message. Assume that the adversary knows the 32-character alphabet used and is capable of recognizing an intelligible message, and the only challenge is arriving on the correct key. Your answer should include the maximum number of guesses required for determining the key, with an explanation for how you determined this number.

- 5. Consider a cryptanalytic approach to breaking the affine Caesar cipher. Specifically, assume that an adversary can mount a finite number of successful chosen plaintext attacks, where they have the ability to determine the ciphertext character corresponding to a plaintext character of their choice.

Explain how these attacks can be used to break the cipher. Your answer should include the number of attacks necessary for breaking the cipher, with an explanation for how you determined this number.